公司新闻

高/低电路重置的基本逻辑和实际陷阱

作者: 365bet体育 点击次数: 发布时间: 2025-06-08 09:48

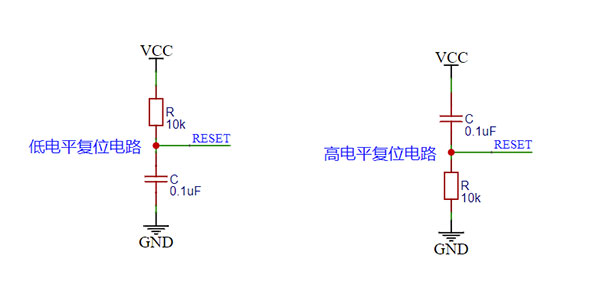

在嵌入式系统设计中,电路重置的极性选择直接决定了设备的功率稳定性。根据统计数据,23%的硬件故障是由信号异常引起的(数据来源:2024 IEEE IEE ICET),并且在电路结构,噪声安全性,芯片灵活性等方面存在重要差异。本文通过实验数据显示了两种设计的深层逻辑。 The address mentioned in this article: ● Core Structure: 10kΩ pull -up resistor + 100nf grounding capacitor (Fig. 1a) ● Startup Timing: Mathematics Formula T_ {Reset} = -RC LN (Frac {V_ {IL}} {V_ {CC}}) Risistor + 100NF Connected VCC Capacitor (Fig. 1b) ● Equation of Start: Mathematics Formula T_ {Reset} = RC LN (Frac {V_ {CC}} {V_ {CC} -V_ {IH}) (standard value: 25ms@VCC = 5V)Tub: VCC = 5V, C = 100NF) * Design warning: If the NRST PIN of the STM32 is incorrectly reset with a high level, it will increase the risk of通过测试(IEC 61000-4-2)通过测试锁定功率:●低循环它重置水平:电磁干扰)(VCC - 错误重置的触发)●加强设计:添加电视二极管,压缩了0.5%经典设计陷阱的错误速率:GD32F303重置悲剧。对工业批次批次的特定综述:现象:固定在设备上的功率是由5%的电路重置引起的:电路重置使用1μF电容器(制造商推荐的100NF)机制:长时间重置(200ms)在警卫队时引起解决方案:RepreAtionFormula:ExteAtionFormula及失败速率,并且要重置为Zero。当工程师在10kΩ电阻和100NF电容器之间做出选择时,它实际上发现了系统的可靠性和成本之间的平衡。低水平的重置主要是随着抗功率供应波动的更好波动,而在对比度系统中,高级重置仍不会代替。真正的专家知道如何在RE图表中阅读电子系统生活的最突出密码设置芯片数据表的时间。

在嵌入式系统设计中,电路重置的极性选择直接决定了设备的功率稳定性。根据统计数据,23%的硬件故障是由信号异常引起的(数据来源:2024 IEEE IEE ICET),并且在电路结构,噪声安全性,芯片灵活性等方面存在重要差异。本文通过实验数据显示了两种设计的深层逻辑。 The address mentioned in this article: ● Core Structure: 10kΩ pull -up resistor + 100nf grounding capacitor (Fig. 1a) ● Startup Timing: Mathematics Formula T_ {Reset} = -RC LN (Frac {V_ {IL}} {V_ {CC}}) Risistor + 100NF Connected VCC Capacitor (Fig. 1b) ● Equation of Start: Mathematics Formula T_ {Reset} = RC LN (Frac {V_ {CC}} {V_ {CC} -V_ {IH}) (standard value: 25ms@VCC = 5V)Tub: VCC = 5V, C = 100NF) * Design warning: If the NRST PIN of the STM32 is incorrectly reset with a high level, it will increase the risk of通过测试(IEC 61000-4-2)通过测试锁定功率:●低循环它重置水平:电磁干扰)(VCC - 错误重置的触发)●加强设计:添加电视二极管,压缩了0.5%经典设计陷阱的错误速率:GD32F303重置悲剧。对工业批次批次的特定综述:现象:固定在设备上的功率是由5%的电路重置引起的:电路重置使用1μF电容器(制造商推荐的100NF)机制:长时间重置(200ms)在警卫队时引起解决方案:RepreAtionFormula:ExteAtionFormula及失败速率,并且要重置为Zero。当工程师在10kΩ电阻和100NF电容器之间做出选择时,它实际上发现了系统的可靠性和成本之间的平衡。低水平的重置主要是随着抗功率供应波动的更好波动,而在对比度系统中,高级重置仍不会代替。真正的专家知道如何在RE图表中阅读电子系统生活的最突出密码设置芯片数据表的时间。 新闻中心

ued在线注册

QQ:88889999

电话:020-66889888

传真:020-66889777

邮箱:admin@admin.com

地址: 广东省广州市番禺经济开发区58号